#### **DS50EV401-EVK User Guide**

#### 2.5 Gbps / 5.0 Gbps / 8.0 Gbps Quad PCI Express Cable and PC Board Equalizer

#### Overview

The DS50EV401-EVK evaluation board provides a typical PCIe application for the evaluation of the DS50EV401 2.5 Gbps, 8 Gbps x4 Lane Serial PCI Express Equalizer.

#### **Specifications**

**DC Input Power (JP1):**  $3.3V \pm 10\%$ , or  $2.5V \pm 5\%$

**Serial Data Inputs (IN\_[0:3] +/- ):** High-speed CML inputs. Acceptable data input speed DC – 8 Gbps. *For more details, please refer to the datasheet.*

**Serial Data Outputs (OUT\_[0:3] +/- ):** High-speed CML outputs. Each output is matched with it's respective input channel. For instance, IN\_0+ input routes to OUT\_0+. *For more details, please refer to the datasheet.*

CML Input Voltage: -0.5V to 4.0V CMOS Input Voltage: -0.5V to 4.0V

### **Jumper Settings**

JP5, JP6, JP7, JP8, JP9, JP10, JP11, JP12 (SD[0:3] / EN[0:3] ): Leave these jumpers unconnected. JP3 (BST1/MODE): The jumper controls equalization frequency levels. Please see Table 1.

**Table 1. Equalization Boost Controls**

| 6 mil microstrip FR4 trace length (in) | 24 AWG Twin-AX cable length (m) | Frequency | Channel Loss | MODE        |

|----------------------------------------|---------------------------------|-----------|--------------|-------------|

| 30                                     | 7                               | 8 Gbps    | 16 dB        | 0 (Default) |

| 40                                     | 10                              | 2.5 Gbps  | 14 dB        | 1           |

|                                        |                                 | 5 Gbps    | 20 dB        |             |

JP2, JP4 (BST0, BST2): DO NOT USE THESE JUMPERS

JP13, JP14, JP15, JP16 (CS, SDC, SDA, FEB): DO NOT USE THESE JUMPERS

**D1**, **D2**: D1/D2 is a LIST-C155KGJRKT LED lamp. The LED serves as the detecting signaling, when shorting pin 1 and 2 of JP5, JP6, JP7, JP8, JP9, JP10, JP11, and JP12. When LED is green/red, the SD is detecting an input signal, and the data channel is at an active mode.

## **Bill of Materials**

| DESIGNATION                       | QTY | DESCRIPTION                          |

|-----------------------------------|-----|--------------------------------------|

| C1, C3, C5, C7                    | 4   | 0.01uF ±10% Ceramic Capacitor 0402   |

| C2, C4, C6, C8, C11, C12, C13,    |     |                                      |

| C14, C15, C16, C17, C18, C19,     |     |                                      |

| C20, C21, C22, C23, C24, C25, C26 | 20  | 0.1uF ±10% Ceramic Capacitor 0402    |

| C9                                | 1   | 4.7uF ±10% Ceramic Capacitor 0805    |

| C10                               | 1   | 22uF ±10% Tan Capacitor 7343         |

| D1, D2                            | 2   | LIST-C155KGJRKT LED lamp             |

| JP1                               | 1   | 1 x 4 Pin Header                     |

| JP2, JP3, JP4, JP13,              |     |                                      |

| JP14, JP15, JP16                  | 7   | 1 x 3 Pin Header                     |

| JP5, JP6, JP7, JP8,               |     |                                      |

| JP9, JP10, JP11, JP12             | 8   | 1 x 2 Pin Header                     |

|                                   |     |                                      |

| JP2, JP4, JP5, JP6, JP12          | 5   | 3 Pin Header                         |

| JP3                               | 1   | 3X2 Pin Header                       |

| JP7                               | 1   | 4X2 Pin header                       |

| J1, J2, J3, J4, J5, J6, J7, J8,   |     |                                      |

| J9, J10, J11, J12, J13, J14, J15, |     |                                      |

| J16,                              | 16  | SMA Edge Tab Receptacle 142-0701-851 |

| R1, R2, R3, R4                    | 4   | 220 ohm Resistors                    |

| U1                                | 1   | National DS50EV401                   |

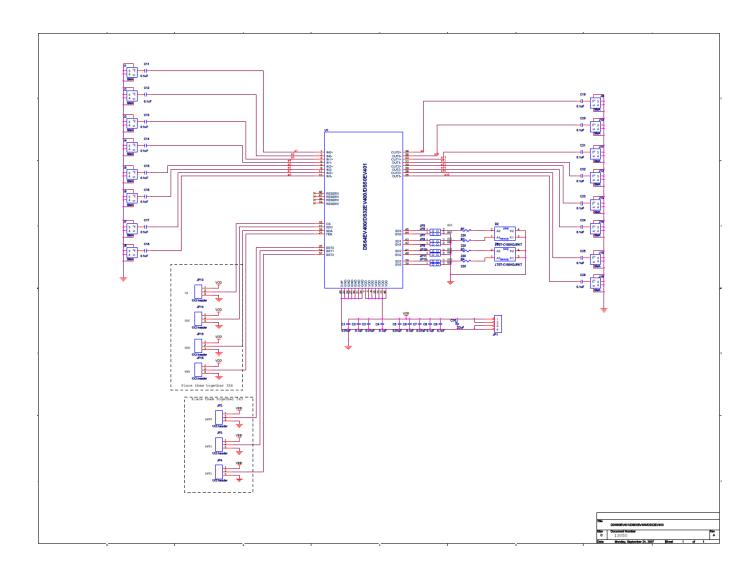

# **Schematics**

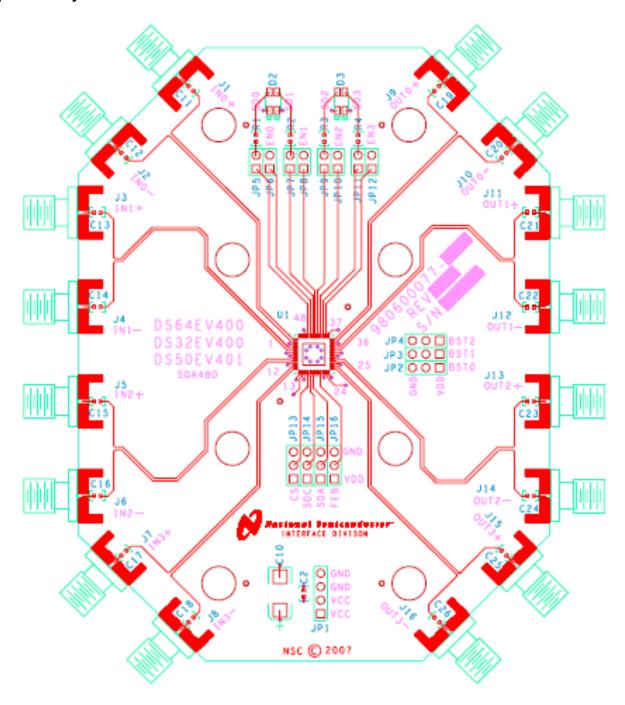

# **Top View Layout**

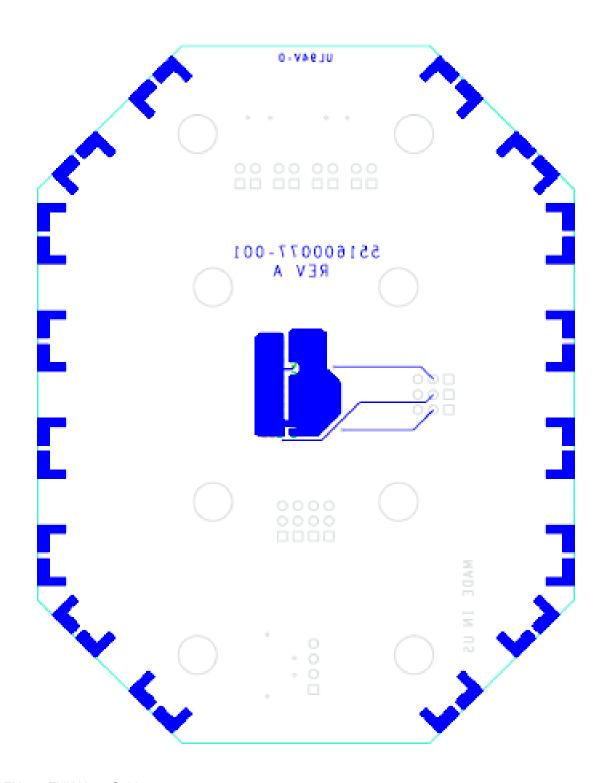

# **Bottom View Layout**